### Intel® PXA255 Processor

Specification Update

September, 2003

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The Intel® PXA255 processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AlertVIEW, i960, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, Commerce Cart, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, GatherRound, i386, i486, iCat, iCOMP, Insight960, InstantlP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel ChatPad, Intel Create&Share, Intel Dot.Station, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetStructure, Intel Play, Intel Play logo, Intel Pocket Concert, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel WebOutfitter, Intel Xeon, Intel Xscale, Itanium, JobAnalyst, LANDesk, LanRover, MCS, MMX, MMX logo, NetPort, NetportExpress, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, ProShare, RemoteExpress, Screamline, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, This Way In, TokenExpress, Trillium, Vivonic, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © Intel Corporation, 2003

\*Third-party brands and names are the property of their respective owners.

# int<sub>e</sub>l<sub>®</sub> Contents

| Revision History                                 | 5    |

|--------------------------------------------------|------|

| Preface                                          | 6    |

| Affected Documents/Related Documents             | 7    |

| General Information<br>PXA255 Processor Markings |      |

| Summary of Changes                               | 9    |

| Codes Used in Summary Table                      | 9    |

| Errata                                           | . 13 |

| Specification Changes                            | . 22 |

| Specification Clarifications                     | . 23 |

| Documentation Changes                            | . 24 |

## **Revision History**

| Date of<br>Revision | Version | Description                                                               |

|---------------------|---------|---------------------------------------------------------------------------|

| September<br>2003   | -007    | Added previous document changes.<br>Modified errata 31<br>Added errata 32 |

| July 2003           | -006    | Added documentation change 14 (deleted old changes 1-13)                  |

| May 2003            | -005    | Added documentation change 1 (13)                                         |

| April 2003          | -004    | Added documentation changes 9, 10, 11, 12                                 |

| March<br>2003       | -003    | Added errata 31<br>Added documentation changes 6, 7, 8                    |

| February<br>2003    | -002    | Added errata 30<br>Added documentation changes 1, 2, 3, 4, 5              |

| January<br>2003     | -001    | Initial release of the Intel® PXA255 Processor                            |

### **Preface**

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

We have endeavored to include all documented errata in the consolidation process; however, we make no representations or warranties concerning the completeness of the Intel® PXA255 Processor Specification Update. This document may also contain information that was not previously published.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

### **Affected Documents/Related Documents**

| Title                                                                      | Order  |

|----------------------------------------------------------------------------|--------|

| Intel® PXA255 Processor Developer's Manual                                 | 278693 |

| Intel® PXA255 Processors Design Guide                                      | 278694 |

| Intel® PXA255 Processors Electrical, Mechanical, and Thermal Specification | 278695 |

# int<sub>el</sub>®

### Nomenclature

**Errata** are design defects or errors. These may cause the Intel® PXA255 Processor (PXA255 processor) behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices unless otherwise noted.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These changes will be incorporated in the next release of the document.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the document.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in the next release of the document.

*Note:* Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

### **General Information**

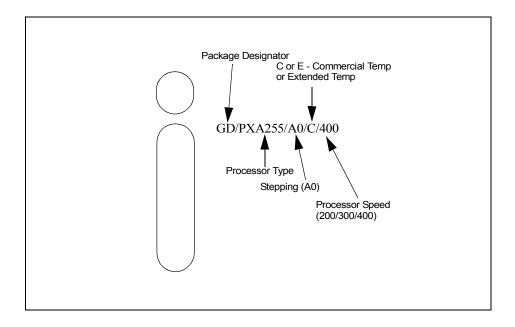

### **PXA255 Processor Markings**

### **Summary of Changes**

The following tables indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the PXA255 processor. Intel may fix some of the errata in a future stepping of the component and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

### **Codes Used in Summary Table**

| X:                           | Errata exists in the stepping indicated. Specification change or clarification that applies to this stepping. |

|------------------------------|---------------------------------------------------------------------------------------------------------------|

| (No mark) or (Blank<br>box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |

| Plan Fix:                    | This erratum may be fixed in a future stepping of the product.                                                |

| Fixed:                       | This erratum has been previously fixed.                                                                       |

| No Fix:                      | There are no plans to fix this erratum.                                                                       |

| Doc:                         | Intel intends to update the appropriate documentation in a future revision.                                   |

| Shaded:                      | This item is either new or modified from the previous version of the document.                                |

|     |            |              | Su     | mmary of Errata (Sheet 1 of 2)                                                                                                      |

|-----|------------|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|

| NO. | <b>A</b> 0 | Refer<br>to: | Status | ERRATA                                                                                                                              |

| 1   | Х          | 13           | No Fix | "MultiMediaCard Stream Data Writes Do Not Transmit Properly"                                                                        |

| 2   | х          | 13           | No Fix | "Watchdog Reset Causes The Real Time Clock (RTC) To Increment<br>At The Wrong Frequency"                                            |

| 3   | х          | 13           | No Fix | "Drain Write Buffer Command Does Not Force All Memory Requests<br>Out To The External Bus"                                          |

| 4   | х          | 14           | No Fix | "Unindexed Mode LDC/STC Instructions Can Corrupt Protected Registers"                                                               |

| 5   | х          | 14           | No Fix | "Aborted Store That Hits the Data Cache Marks Write-back Data Dirty"                                                                |

| 6   | Х          | 14           | No Fix | "MAC Instructions May Not Be Executed During Debug Mode"                                                                            |

| 7   | х          | 14           | No Fix | "A Load That Follows a DTLB Invalidate Entry Command Will Also<br>Be Invalidated."                                                  |

| 8   | Х          | 15           | No Fix | "Jtag Highz Instruction Not 1149.1 Compliant"                                                                                       |

| 9   | Х          | 15           | No Fix | "Instruction Fetch Unit (IFU) Misses an External Abort"                                                                             |

| 10  | х          | 15           | No Fix | "SDRAM Auto Power Down Does Not Shut Off SDCLKs 0, 1, and 2<br>When Their Respective Partitions Are Not Being Accessed"             |

| 11  | х          | 15           | No Fix | "Memory Controller GPIO Pins Float High After Reset and Cause a Write to Address 0x0"                                               |

| 12  | х          | 16           | No Fix | "The SPI Protocol In The MMC Is Giving CRC Errors On Every<br>Commands Response."                                                   |

| 13  | Х          | 16           | No Fix | "MMC Compatibility issue with different brand MMC cards."                                                                           |

| 14  | х          | 16           | No Fix | "MMC SPI mode – if card is deselected, PROG_DONE will not be set."                                                                  |

| 15  | х          | 16           | No Fix | "AC97 Transmits invalid data on the PXA255 processor with 66Mhz Core/33Mhz Memclk."                                                 |

| 16  | х          | 17           | No Fix | "Long idle time on external bus between DREQ and nCS for flow-through DMA."                                                         |

| 17  | х          | 17           | No Fix | "MMC - invalid data can be written to card if user stops then restarts the clock prior to end of data transfer."                    |

| 18  | х          | 17           | No Fix | "PMU monitoring event #1, cycles in which the I-cache cannot<br>deliver an instruction, is incorrectly incremented"                 |

| 19  | х          | 17           | No Fix | "In Special Debug State, back to back memory transactions may<br>hang if the first memory operation receives a precise data abort." |

| 20  | х          | 18           | No Fix | "The first access to a disabled SDRAM partition will not do a refresh cycle."                                                       |

| 21  | х          | 18           | No Fix | "Error occurs if memory access starts within last 32 bytes of a 64MB region of static/PCMCIA memory."                               |

| 22  | х          | 18           | No Fix | "Overrun on the Receive FIFO for the PCM channel of the AC97 unit will leave the FIFOs in an unrecoverable state."                  |

| 23  | х          | 19           | No Fix | "SET_FEATURE/CLEAR_FEATURE Request with an illegal feature selector value will cause the UDC controller to respond incorrectly."    |

| 24  | х          | 19           | No Fix | "The JTAG Controller must have the 3.6864 MHz oscillator running to work."                                                          |

|     |           |              | Su     | mmary of Errata (Sheet 2 of 2)                                                                                    |

|-----|-----------|--------------|--------|-------------------------------------------------------------------------------------------------------------------|

| NO. | <b>A0</b> | Refer<br>to: | Status | ERRATA                                                                                                            |

| 25  | Х         | 19           | No Fix | "DMA accesses to 8bit PCMCIA I/O space cause additional reads."                                                   |

| 26  | х         | 19           | No Fix | "Indeterminate results may occur in certain peripherals during a Frequency change if they are active"             |

| 27  | х         | 20           | No Fix | "Slow IrDA Transmit pulse width cropped when SET BREAK is used"                                                   |

| 28  | Х         | 20           | No Fix | "Fast Infrared FIR mode fails IrDA spec"                                                                          |

| 29  | х         | 20           | No Fix | "Asserting MBREQ during the MRS command transfer can cause SDRAM data corruption"                                 |

| 30  | Х         | 20           | No Fix | "Invalid AC'97 interrupt during cold reset"                                                                       |

| 31  | х         | 21           | No Fix | "GPIO output signals, memory address pins and the memory controls pins, nOE and nWE, are unpredictable in sleep." |

| 32  | х         | 21           | No Fix | "Non-branch instruction in vector table may execute twice after a thumb mode exception"                           |

|     |            |              | Sum        | mary of Specification Changes              |

|-----|------------|--------------|------------|--------------------------------------------|

| NO. | <b>A</b> 0 | Refer<br>to: | Status     | Specification Changes                      |

|     |            | N            | OTE: There | are no specification changes at this time. |

|     | Su                | immary o     | of Specifica | ation Clarifications         |

|-----|-------------------|--------------|--------------|------------------------------|

| NO. | Document Revision | Refer<br>to: | Status       | Specification Clarifications |

|     | NOTE: T           | here are     | no specific  | ation changes at this time.  |

|     | Summa                        | ry of Doc    | cumentation Changes (Sheet 1 of 2)                                                               |

|-----|------------------------------|--------------|--------------------------------------------------------------------------------------------------|

| NO. | Document Revision            | Refer<br>to: | Documentation Changes                                                                            |

| 1   | 278693<br>Developer's Manual | 24           | "The physical address of the Divisor Latch Register High (DLH)<br>Bit Definitions is incorrect." |

| 2   | 278693<br>Developer's Manual | 24           | "ROR bit should reset when SSE Bit is cleared"                                                   |

| 3   | 278693<br>Developer's Manual | 24           | "End/Error in FIFO' interrupt occurs at or below trigger level"                                  |

| 4   | 278693<br>Developer's Manual | 25           | "Alternate interface settings not supported in USB."                                             |

| 5   | 278693<br>Developer's Manual | 25           | "Alternate interface settings not supported in USB."                                             |

# int<sub>el</sub>®

|     | Summary of Documentation Changes (Sheet 2 of 2) |              |                                                                                           |  |  |

|-----|-------------------------------------------------|--------------|-------------------------------------------------------------------------------------------|--|--|

| NO. | Document Revision                               | Refer<br>to: | Documentation Changes                                                                     |  |  |

| 6   | 278693<br>Developer's Manual                    | 25           | "GPIO Reset Procedure"                                                                    |  |  |

| 7   | 278693<br>Developer's Manual                    | 26           | "GPIO 28 - AC'97 bit_clk can only be an input"                                            |  |  |

| 8   | 278693<br>Developer's Manual                    | 26           | "PKG_TYPE Incorrect"                                                                      |  |  |

| 9   | 278693<br>Developer's Manual                    | 26           | "GPIOs in Section 4.1"                                                                    |  |  |

| 10  | 278693<br>Developer's Manual                    | 27           | "Mislabeled bits 1:0 in Table 12-13 header"                                               |  |  |

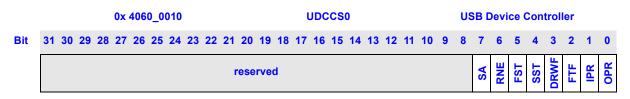

| 11  | 278693<br>Developer's Manual                    | 27           | "Mislabeled OPR bit description in Table 12-14"                                           |  |  |

| 12  | 278693<br>Developer's Manual                    | 28           | "The reset bits for Table 12-13 UDC Control Function Register were numbered incorrectly." |  |  |

| 13  | 278693<br>Developers Manual                     | 29           | "Mislabeled RSP bit description in Table 12-18"                                           |  |  |

| 14  | 278693<br>Developers Manual                     | 30           | "Replaced Table 12-13."                                                                   |  |  |

# int<sub>el®</sub> Errata

| 1.           | MultiMediaCard Stream Data Writes Do Not Transmit Properly                                                                                                                                                                                            |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | MultiMediaCard stream data writes of length equal to $(n*32)+6$ bytes, where n=1,2,3,etc., do not transmit properly. The MMC card does not receive one of the bytes but it does receive the stop command.                                             |

| Implication: | When the MMC unit transmits $(n*32)+6$ bytes, the MMC card actually receives $(n*32)+5$ bytes. It is impossible to determine which byte is missing.                                                                                                   |

| Workaround:  | Driver software must break up stream data writes equal to $(n*32)+6$ bytes into separate transactions that are not equal to $(n*32)+6$ .                                                                                                              |

| Status:      | No Fix                                                                                                                                                                                                                                                |

| 2.           | Watchdog Reset Causes The Real Time Clock (RTC) To Increment At The Wrong Frequency                                                                                                                                                                   |

| Problem:     | When a watchdog reset occurs, the internal logic that uses the RTC Trim Register (RTTR) values to set the frequency of the RTC become out of sync and no longer increment the RTC at the correct frequency.                                           |

| Implication: | The RTC clock value (RCNR) becomes invalid because the RTC no longer increments at the correct frequency after watchdog resets.                                                                                                                       |

| Workaround:  | After every watchdog reset:                                                                                                                                                                                                                           |

|              | • If the lock bit is not set in the RTTR register, write the appropriate value to the RTTR register and then write the appropriate value to the RCNR register.                                                                                        |

|              | • If the lock bit is set in the RTTR register, do a dummy write to the RTTR register to resync the internal logic to the original RTTR value that was written before the lock bit was set, and then write the appropriate value to the RCNR register. |

| Status:      | No Fix                                                                                                                                                                                                                                                |

| 3.           | Drain Write Buffer Command Does Not Force All Memory Requests Out To The External Bus                                                                                                                                                                 |

| Problem:     | Whether there are outstanding memory requests in the execution pipeline or not the drain write<br>buffer command does not correctly force all outstanding memory requests completely out to the<br>external bus.                                      |

| Implication: |                                                                                                                                                                                                                                                       |

| Workaround:  | Two workarounds are available to ensure a write propagates out to the external bus.                                                                                                                                                                   |

|              | • Perform a read back from the same location that just written to.                                                                                                                                                                                    |

|              | • Perform any transaction to a memory page marked X=C=B=0 (IO cycle).                                                                                                                                                                                 |

|              | Both workarounds ensure all previous memory transactions complete before execution begins on any subsequent instructions.                                                                                                                             |

| Status:      | No Fix                                                                                                                                                                                                                                                |

Errata

| 4.           | Unindexed Mode LDC/STC Instructions Can Corrupt Protected Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | Unindexed mode LDC or unindexed mode STC can corrupt protected registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Implication: | This error can be seen in any of the following scenarios:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|              | • During the execution of an LDC instruction, FIQ mode registers r8-r14 and debug mode register r13 could be corrupted                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | • During the execution of an STC instruction, Rn could be corrupted                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              | <ul> <li>Memory locations could be corrupted based on the base register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Workaround:  | Do not use unindexed addressing for LDC or STC instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.           | Aborted Store That Hits the Data Cache Marks Write-back Data Dirty                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Problem:     | An aborted store that hits in the data cache does not modify the contents of the data cache but the dirty bit for that cache line is set.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Implication: | If there is no other external bus master in the system that will be sharing memory regions with the processor, this erratum will simply write-back data out to external memory, even though the data really was not modified. In normal operation this will be nothing more than an extra store on the bus that writes the same data to memory that is already there.                                                                                                                                                                          |

|              | If another bus master in the system exists, this erratum manifests itself in the following manner. The processor loads in a cache line from a memory region shared with another bus master. The external bus master modifies the same line in external shared memory. The processor attempts to modify data in the cache line, hits the cache, aborts because of MMU permissions, the data is not modified, but sends the dirty bit. When the cache line is evicted, the original data overwrites any data written by the external bus master. |

| Workaround:  | Use one of the following suggestions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              | Mark shared memory as write-through                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              | • Use semaphores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | • Use other handshaking techniques to prevent collisions on shared memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.           | MAC Instructions May Not Be Executed During Debug Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Problem:     | MAC instructions may not be executed during debug mode. When the processor goes into the debug handler and enters a special debug state, MAC instructions are not executed if another exception occurs. The debug handler does not have any indication that the MAC instruction did not execute.                                                                                                                                                                                                                                               |

| Implication: | The accumulator does not update properly or have the correct value because the MAC instruction does not execute.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Workaround:  | Disable debug in the Debug Control and Status Register (DCSR) before doing a MAC instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7.           | A Load That Follows a DTLB Invalidate Entry Command Will Also Be Invali-<br>dated.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Problem:     | If a load or store instruction immediately follows an Invalidate Data Translation Look-aside Buffer (DTLB) Entry command (mcr p15, 0, Rd, c8, c6, 1) and the page table entry required by the load/ store instruction is resident in the data TLB, the load/store entry will be invalidated along with the                                                                                                                                                                                                                                     |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Errata

target of the Invalidate D-TLB entry command. This can also occur if one instruction with an issue latency of one cycle is executed after the Invalidate D-TLB entry command and before the load/ store instruction.

| Implication: |                                                                                                                                                                                                                                                                                                                                                     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Workaround:  | Follow all DTLB Invalidate Entry commands with two no-ops.                                                                                                                                                                                                                                                                                          |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                              |

| 8.           | Jtag Highz Instruction Not 1149.1 Compliant                                                                                                                                                                                                                                                                                                         |

| Problem:     | JTAG HIGHZ instruction is not IEEE 1149.1 compliant.                                                                                                                                                                                                                                                                                                |

| Implication: | The processor violates the IEEEE 1149.1 specification because it places the outputs into an inactive state one clock after the HIGHZ instruction.                                                                                                                                                                                                   |

| Workaround:  | Insert an extra clock after the HIGHZ instruction to three-state the pads.                                                                                                                                                                                                                                                                          |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                              |

| 9.           | Instruction Fetch Unit (IFU) Misses an External Abort                                                                                                                                                                                                                                                                                               |

| Problem:     | If a bus abort occurs on a code fetch while a Instruction Translation Look-aside Buffer (I-TLB) lock instruction is outstanding, the IFU fails to abort. Instead, the IFU will execute the instruction returned on the aborting transaction. This problem does not affect parity errors.                                                            |

| Implication: |                                                                                                                                                                                                                                                                                                                                                     |

| Workaround:  | Execute the instruction Sub pc, pc #4 after every I-TLB or I-Cache lock command. The Sub pc, pc #4 instruction is not predicted, which causes the pipeline to be flushed.                                                                                                                                                                           |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                              |

| 10.          | SDRAM Auto Power Down Does Not Shut Off SDCLKs 0, 1, and 2 When Their Respective Partitions Are Not Being Accessed                                                                                                                                                                                                                                  |

| Problem:     | If MDREFR[APD] is set, the processor does not shut off the appropriate SDCLKs when their respective partitions are not being accessed. This causes no functional problems.                                                                                                                                                                          |

| Implication: | When the core accesses any SDRAM partition, all SDCLKs (i.e., SDCLK<2:0>) come on, and all SDCLKs stay on until the core does not need to access any of the SDRAM partitions.                                                                                                                                                                       |

| Workaround:  | None                                                                                                                                                                                                                                                                                                                                                |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                              |

| 11.          | Memory Controller GPIO Pins Float High After Reset and Cause a Write to Address 0x0                                                                                                                                                                                                                                                                 |

| Problem:     | When a hard reset occurs, the address bus is driven to 0x0. If a hard reset is asserted during a static chip select write cycle, the address bus is driven to 0x0 quickly but nCSx and nWE return to the deasserted state more slowly which means a write to address 0x0 can occur. This is evident with all static memory devices, PCMCIA, and CF. |

| Implication: | If a hard reset is asserted, the address bus is 0x0 while the chip select pin and write enable pin is still asserted. Any data at address 0x0 could be overwritten with random data.                                                                                                                                                                |

| Workaround:  | None                                                                                                                                                                                                                                                                                                                                                |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                              |

Errata

### 12. The SPI Protocol In The MMC Is Giving CRC Errors On Every Commands Response.

**Problem:** If the cyclic redundancy check (CRC) enable bit is set in the SPI register while using the SPI protocol, the MMC controller gives a false "CRC error on response" to every command it sends out. If this CRC error is ignored, the data transfers correctly and there is no CRC error.

Implication:

Workaround: Ignore the CRC error during the command response period.

Status: No Fix

### 13. MMC Compatibility issue with different brand MMC cards.

**Problem:** The X means that the card is compatible in that mode.

| Card |        |       |         |        |          |  |

|------|--------|-------|---------|--------|----------|--|

|      |        | Lexar | Sandisk | Viking | DaneElec |  |

| Mode | SPI    | Х     |         | Х      | Х        |  |

| WOUE | Stream |       | Х       |        |          |  |

|      | Block  | Х     | Х       | Х      | Х        |  |

In stream mode the last 2 bytes are read as zeros in rest of the three cards (other than Sandisk)

Stream mode on Sandisk is seeing an underrun error being returned from the card at the 4 highest speeds. All the rest of the speeds (5-7) are functional.

#### Implication:

Workaround:

Status: No Fix

#### 14. MMC SPI mode – if card is deselected, PROG\_DONE will not be set.

**Problem:** If changing SPI chip selects, the PROG\_DONE bit does not get updated with the state of the selected card.

Implication: If programming card0, then switch to card1, then come back to card0, there is no way of knowing if card0 ever finished programming

**Workaround:** User can tie MMDAT signal to a GPIO and monitor the signal by reading the GPIO status register until the signal goes high.

Status: No Fix

#### 15. AC97 Transmits invalid data on the PXA255 processor with 66Mhz Core/ 33Mhz Memclk.

**Problem:** When the core frequency for PXA255 processor is set to 66MHz, the AC97 transmits invalid data. This is true for both initial state and steady state. Some frames have valid data with valid frame and/or valid channel bits not set. Some frames also contain invalid data. More than 60% of the of the frames are invalid.

Implication:

Workaround: When the core frequency is set to 100MHz, the data is transmitted correctly.

Status: No Fix

| 16.          | Long idle time on external bus between DREQ and nCS for flow-through DMA.                                                                                                                                                                                                          |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | While observing a flow through DMA transaction, DREQ is asserted, then traffic on the SDRAM bus finishes, then there is approximately 500ns (50 SDCLKs) of no activity before the chip select associated with the DMA is asserted. This only occurs once in many DMA transactions. |

|              | The problem was that the internal bus arbiter was being retried due to internal buffers being full.<br>This retry was taking an excessive amount of time.                                                                                                                          |

| Implication: |                                                                                                                                                                                                                                                                                    |

| Workaround:  |                                                                                                                                                                                                                                                                                    |

| Status:      | No Fix                                                                                                                                                                                                                                                                             |

| 17.          | MMC - invalid data can be written to card if user stops then restarts the clock prior to end of data transfer.                                                                                                                                                                     |

| Problem:     | For block writes (single and multiple) it was found that if the user stops the clock and restarts it, say with a CMD12 programmed to stop the data transfer, the MMC can send out bad data to the card.                                                                            |

|              | This only applies to the case where the clock is stopped/started by writing to the MMC_STRPCL register, not when the MMC controller stops/starts the clock based on whether the TX fifo has data in it.                                                                            |

|              | The data corruption does not apply to stream mode writes.                                                                                                                                                                                                                          |

| Implication: | There is no guarantee of the data transfers, response contents, etc. if software turns the clock off before a command and data sequence is complete.                                                                                                                               |

| Workaround:  | Software should never turn the clock off before the end of a command protocol and any data transfer, with the exception of the stop command for stream writes.                                                                                                                     |

| Status:      | No Fix                                                                                                                                                                                                                                                                             |

| 18.          | PMU monitoring event #1, cycles in which the I-cache cannot deliver an instruction, is incorrectly incremented                                                                                                                                                                     |

| Problem:     | The only clock cycles that should be counted for PMU monitoring event #1 are for I-cache misses or I-TLB misses. Many other events may erroneously cause this counter to increment.                                                                                                |

| Implication: |                                                                                                                                                                                                                                                                                    |

| Workaround:  | Do not use PMU monitoring event #1.                                                                                                                                                                                                                                                |

| Status:      | No Fix                                                                                                                                                                                                                                                                             |

| 19.          | In Special Debug State, back to back memory transactions may hang if the first memory operation receives a precise data abort.                                                                                                                                                     |

| Problem:     | Special Debug State (SDS) is used by debug vendors. If a back to back store is used in SDS, and the first store receives a precise data abort, the first memory operation is correctly cancelled, but the second memory operation may leave the core in an unknown state.          |

| Implication: |                                                                                                                                                                                                                                                                                    |

| Workaround:  | While in SDS, any memory operation that may cause a precise data abort must be followed by a Drain Write Buffer command. Load Multiple/Store Multiple that may cause precise data aborts must not be used.                                                                         |

| Status:      | No Fix                                                                                                                                                                                                                                                                             |

| 20.          | The first access to a disabled SDRAM partition will not do a refresh cycle.                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | The first access to a disabled SDRAM partition will not do a refresh cycle. The second and subsequent accesses to a disabled SDRAM partition will perform a refresh cycle. The first access will show up on the bus as a RAS/CAS cycle, but no refresh cycle will proceed it.                                                                                                                                                                          |

| Implication: | When generating refresh cycles by accessing a disabled SDRAM partition, perform two or more accesses to cause one or more refresh cycles.                                                                                                                                                                                                                                                                                                              |

| Workaround:  | Do one more access to any disabled SDRAM partition than planned. For example, if performing 8 refresh cycles to SDRAM, software must do 9 accesses to a disabled SDRAM partition.                                                                                                                                                                                                                                                                      |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 21.          | Error occurs if memory access starts within last 32 bytes of a 64MB region of static/PCMCIA memory.                                                                                                                                                                                                                                                                                                                                                    |

| Problem:     | If the processor accesses, either read or write, the last 32 bytes of a 64MB region of any static chip select region or PCMCIA/CF chip select region, then data corruption will occur. This will effect all six 64MB static memory regions and eight 64MB PCMCIA/CF memory regions. This does not effect SDRAM memory regions.                                                                                                                         |

| Implication: |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Workaround:  | This erratum will not occur if the processor's memory access does not cross a 64MB boundary and within the last 32 bytes of a 64MB static/PCMCIA memory region, any one of the following is performed:                                                                                                                                                                                                                                                 |

|              | • processor only does a byte load or byte store on a byte boundary.                                                                                                                                                                                                                                                                                                                                                                                    |

|              | • processor only does a half-word load or half-word store on a half-word boundary.                                                                                                                                                                                                                                                                                                                                                                     |

|              | <ul> <li>processor only does a word load or word store on a word boundary.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                  |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 22.          | Overrun on the Receive FIFO for the PCM channel of the AC97 unit will leave the FIFOs in an unrecoverable state.                                                                                                                                                                                                                                                                                                                                       |

| Problem:     | If a receive overrun occurs on the AC97 Two-channel composite PCM Receive FIFO, this will stop<br>the channel. The overrun can cause the most significant and least significant 16 bits of the FIFO<br>(i.e. the left channel and right channel) to be switched. If the DMA or core later empties the FIFO,<br>then this switching of data, and therefore invalid data, will continue to occur until the AC97 unit<br>and the FIFO pointers are reset. |

| Implication: | Software should assume that any overrun condition is fatal and that, following the error, the FIFO contents are invalid.                                                                                                                                                                                                                                                                                                                               |

| Workaround:  | If software wishes to manually stop the DMA that services the AC97 Receive FIFO, then first power off the ADC subsystem of the codec, then stop the DMA channel associated with the Receive FIFO. If done quickly enough (8 sample times, 166us at 48kHz), this should avoid the possibility of the Receive FIFO overflow and thus the Left/Right channel swapping.                                                                                    |

|              | If an overrun occurs on the AC97 Receive FIFO, and a Receive FIFO Overrun error in the PCM_In Status Register is indicated, then stop the DMA channel associated with the Receive FIFO, and issue a cold reset to the AC97 circuitry and to the AC97 unit, by setting GCR[COLD_RST] to zero.                                                                                                                                                           |

| Status:      | No Fix                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23.          | SET_FEATURE/CLEAR_FEATURE Request with an illegal feature selector                                                                                                                                                                                        |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | value will cause the UDC controller to respond incorrectly.<br>If the USB host issues a SET/CLEAR feature request with an illegal feature selector value, the UDC controller incorrectly responds to the request with an ACK handshake. The device should |

|              | respond with a STALL.                                                                                                                                                                                                                                     |

| Implication: | Violates the USB 1.1 protocol since the UDC controller responds with an ACK rather than a STALL handshake to the USB host.                                                                                                                                |

| Workaround:  |                                                                                                                                                                                                                                                           |

| Status:      | No Fix                                                                                                                                                                                                                                                    |

| 24.          | The JTAG Controller must have the 3.6864 MHz oscillator running to work.                                                                                                                                                                                  |

| Problem:     | The 3.6864 MHz on-chip oscillator must be running, either from a 3.6864 MHz crystal source or from a 3.6864 MHz clock source, in order for the JTAG Controller to work properly.                                                                          |

| Implication: | The JTAG Controller will not work with just a TCK clock source.                                                                                                                                                                                           |

| Workaround:  | The 3.6864 MHz on-chip oscillator must be running, either from a 3.6864 MHz crystal source or from a 3.6864 MHz clock source, in order for the JTAG Controller to work properly.                                                                          |

| Status:      | No Fix                                                                                                                                                                                                                                                    |

| 25.          | DMA accesses to 8bit PCMCIA I/O space cause additional reads.                                                                                                                                                                                             |

| Problem:     | This erratum is the same as erratum 86 but with the following addition: If DMA is used to access 8bit PCMCIA I/O space, additional reads can be generated if the length in the descriptor is odd.                                                         |

| Implication: |                                                                                                                                                                                                                                                           |

| Workaround:  | Do not use DMA to access to 8bit PCMCIA I/O space. If DMA is used, software must ensure that the descriptor lengths are even.                                                                                                                             |

| Status:      | No Fix                                                                                                                                                                                                                                                    |

| 26.          | Indeterminate results may occur in certain peripherals during a Frequency change if they are active                                                                                                                                                       |

| Problem:     | Indeterminate results may occur in certain peripherals while transmitting or receiving data during a frequency change sequence.                                                                                                                           |

| Implication: |                                                                                                                                                                                                                                                           |

| Workaround:  | If the operation of these peripherals would be adversely affected, then these peripherals would have to be disabled during a frequency change.                                                                                                            |

|              | • MMC                                                                                                                                                                                                                                                     |

|              | • FFUART                                                                                                                                                                                                                                                  |

|              | • STUART                                                                                                                                                                                                                                                  |

|              | • BTUART                                                                                                                                                                                                                                                  |

|              | • IrDA                                                                                                                                                                                                                                                    |

|              | • SSP                                                                                                                                                                                                                                                     |

|              | • UDC                                                                                                                                                                                                                                                     |

|              | • AC97                                                                                                                                                                                                                                                    |

| Status:      | No Fix                                                                                                                                                                                                                                                    |

| 27.                                                                          | Slow IrDA Transmit pulse width cropped when SET BREAK is used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:                                                                     | The Slow IrDA (SIR) port can show errors while transmitting data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |